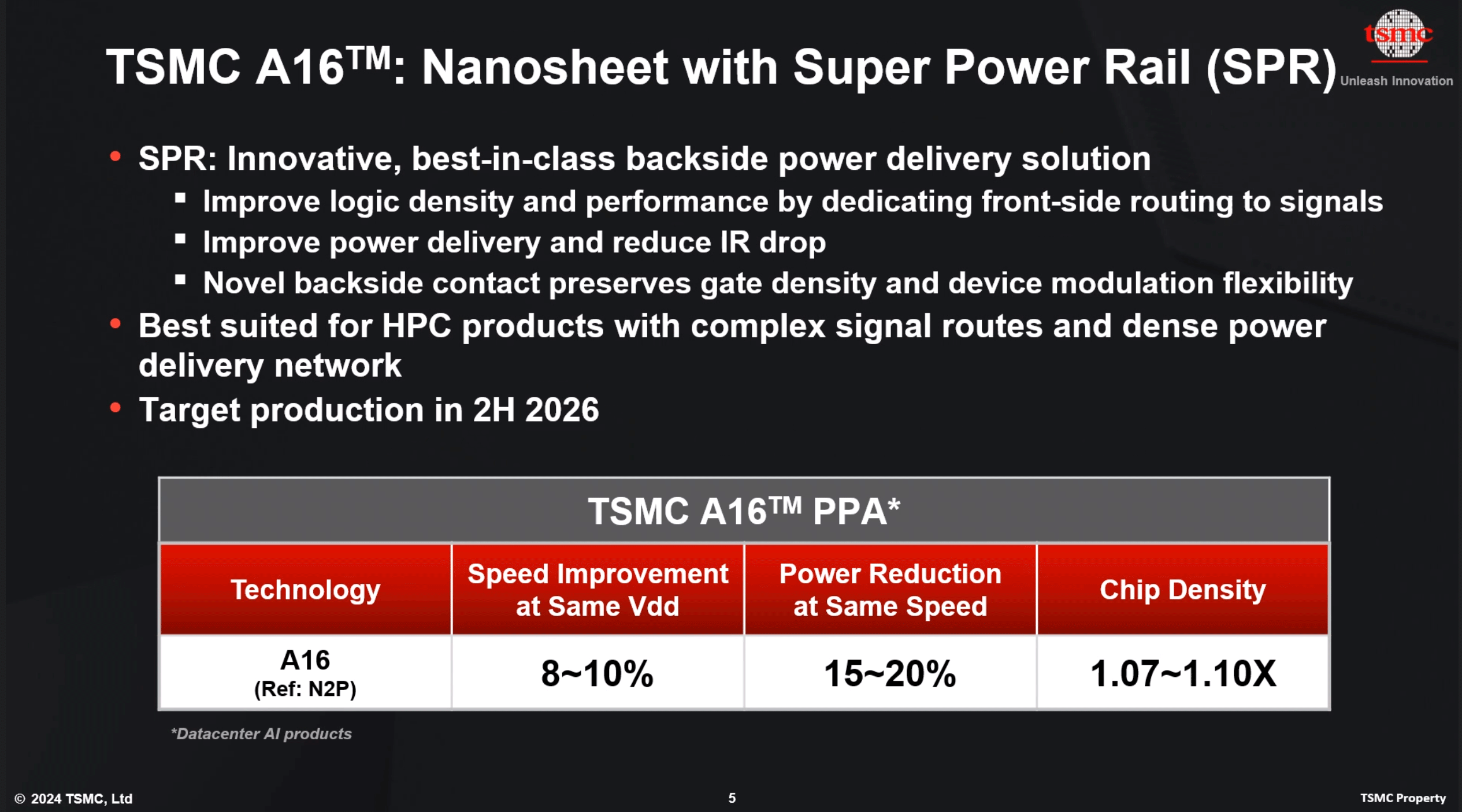

TSMC sedang melakukan pembuatan chip 1,6nm dengan jaringan transfer daya yang efisiensi dan transistor yang lebih padat. Memanfaatkan transistor nanosheet gate-all-around yang mirip dengan arsitektur N2, N2P, dan N2X yang akan datang berdasarkan node 2nm, proses 1,6nm yang baru diumumkan menjanjikan peningkatan clockspeed sebesar 10% pada voltase yang sama dan pengurangan konsumsi daya hingga 20% pada frekuensi dan kompleksitas yang setara. Tergantung pada desain chip, proses baru ini dapat mengakomodasi peningkatan jumlah transistor hingga 10%.

Bisa dibilang, aspek yang paling luar biasa dari chip yang akan datang ini adalah penggabungan jaringan pengiriman daya di bagian belakang. Teknologi ini menjanjikan peningkatan kepadatan transistor dan peningkatan distribusi daya, sehingga berdampak positif pada performa. TSMC memanfaatkan teknologi Super Power Rail (SPR), jenis konektor khusus yang menghubungkan chip ke sumber listrik dan jaringan pengiriman daya bagian belakang akan sangat menguntungkan prosesor AI dan HPC yang memerlukan kabel sinyal rumit dan jaringan listrik padat.

Jadwal produksi generasi pertama chip tersebut ditargetkan pada paruh kedua tahun 2026 dan yang siap dijual pada tahun 2027.